No credit card required

Understands CAD formats

Layer-aware analysis

Vitae dignissim curabitur nascetur nullam fermentum conubia dolor sagittis habitant habitasse ut etiam

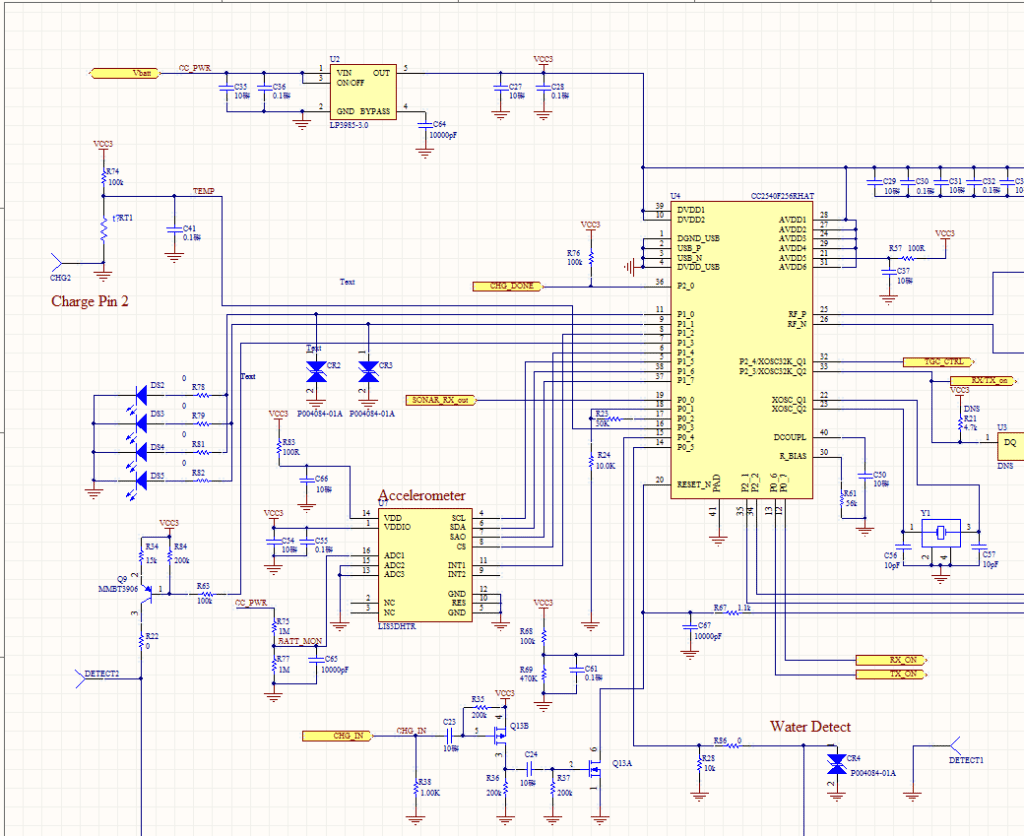

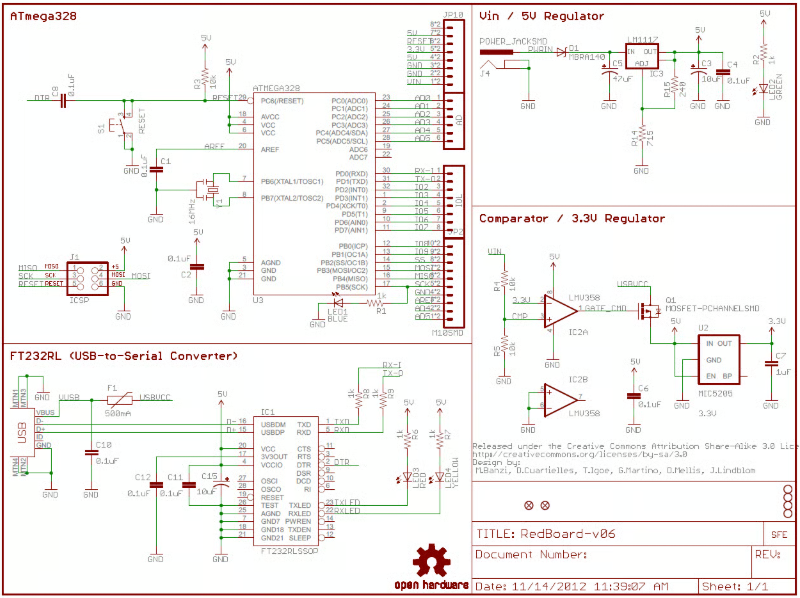

Unlike text-based document analysis, schematic Q&A requires understanding spatial relationships, circuit topology, and engineering intent. Traditional RAG approaches fall short when precision is critical.

In schematic QA, meaning is contextual and spatial — a wrong line thickness, misplaced node, or mislabeled connector can change circuit behavior. Understanding requires reasoning about geometry, topology, and intent simultaneously.

Impact:Semantic errors propagate through entire designs

Manufacturing and semiconductor diagrams vary massively by vendor, CAD system, and layer stack. Unlike textual QA with standardized templates, schematic QA faces non-uniform symbols, annotation styles, and proprietary drawing layers.

Impact:Supervised learning and generalization becomes extremely difficult

Visual QA must blend vision + text + logic. Questions like 'does this net connect the same component across layers?' require structural reasoning across hierarchies and 2D spatial relationships.

Impact:Single-modal models cannot capture cross-layer dependencies

A single misplaced node or mislabeled trace can cost millions in rework or downtime. Schematic QA requires semantic correctness — every connection, label, and symbol must align with engineering intent.

Impact:Production failures from schematic errors cost $2M+ per incident

Circuit topology and component hierarchies

Multi-layer spatial relationships

Vendor-specific symbol libraries

Engineering design intent and constraints

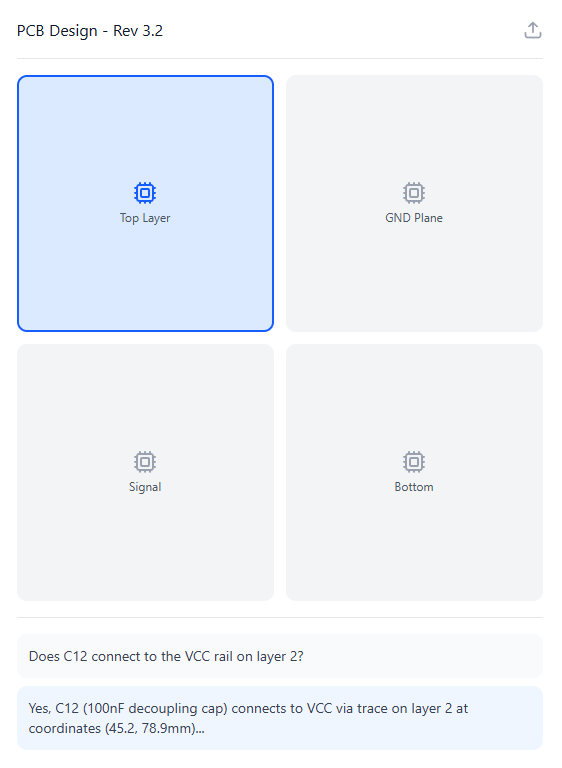

Intuitive two-panel interface with drag-and-drop uploads, topology-aware analysis, and enterprise-grade security for your most sensitive designs.

Ask about circuit connections, component relationships, and net paths. Understands how elements connect across layers.

Upload schematics from Altium, Eagle, KiCad, OrCAD, and more. Preserves layer information and metadata.

Analyze multi-layer PCBs with understanding of signal, power, and ground planes. Track vias and cross-layer connections.

Every answer includes visual highlights showing exact component locations and connection paths in your schematic.

Upload entire design packages and ask questions that span multiple sheets, hierarchies, and sub-circuits.

GDPR, ISO 27001, SOC 2, NIST AI RMF compliant. Your proprietary designs stay confidential and secure.

Understands vendor-specific symbols, custom components, and non-standard annotations across different CAD systems.

Organize schematics by project, revision, or design phase with searchable thumbnails and version tracking.

Intuitive two-panel interface with drag-and-drop uploads, topology-aware analysis, and enterprise-grade security for your most sensitive designs.

Built with a clean two-panel interface designed for engineering workflows. Keep your schematics organized on one side while asking topology-aware questions on the other.

From semiconductor design to manufacturing floor, Visual Q&A helps engineering teams validate designs, prevent costly errors, and accelerate review cycles.

Review PCB layouts, validate signal integrity, and verify component connections. Ask 'does pin 7 of U3 connect to ground?' and get precise answers with visual highlights.

Analyze IC schematics, verify power distribution networks, and validate clock trees. Understand multi-layer routing and cross-reference against design specs.

Validate assembly drawings, check Bill of Materials against schematics, and identify potential manufacturing issues before production starts.

Automate schematic reviews against design rules, verify net connections, and catch errors that could cost millions in production delays or recalls.

Designed for semiconductor and electronics companies handling sensitive design IP. We adhere to industry-leading security standards, ensuring your proprietary schematics and PCB designs are protected with the highest level of data integrity and confidentiality.

Compliant

Certified

Type II

Aligned

Secure

End-to-end encryption for schematics, design files, and all AI model interactions

Keep your design IP within your infrastructure with air-gapped deployment options

Complete version tracking and access logs for regulatory and IP protection compliance

Join engineering teams who trust Visual Q&A to validate critical schematic designs

Engineering Teams

Schematics Analyzed

In Prevented Errors

Detection Accuracy